ETL Mark Ⅱ用リレー

|

|

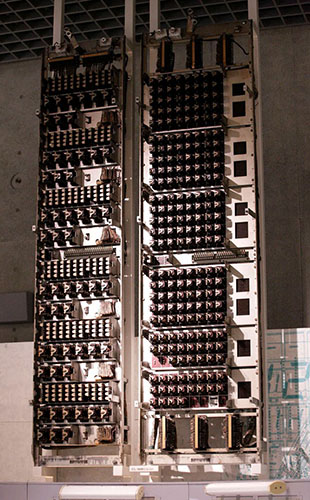

計算機本体

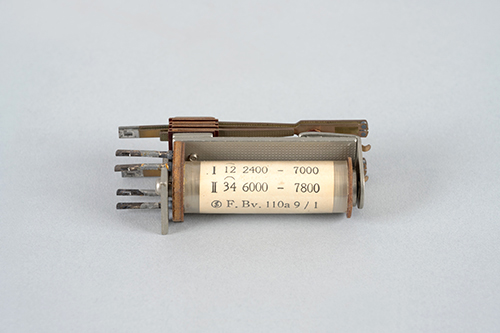

1bit記憶リレー(S型) 主として記憶回路用。接点数は少なくてよいが、動作が速いこと、消費電力は少ないことが求められた。 |

|

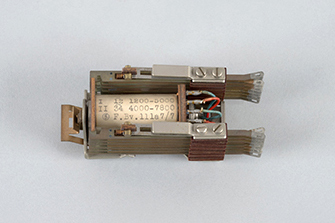

演算リレー(C型) 主として演算回路・制御回路用。演算が終われば切るので消費電力は多少多くてもよいが、接点は多く、動作時間も速いことが求められた。 |

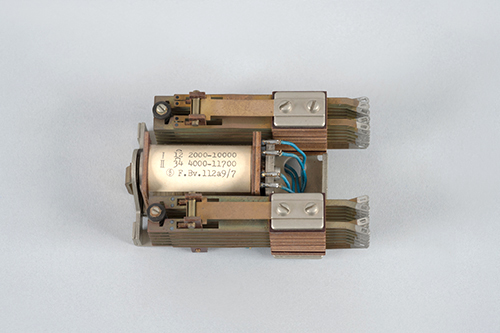

ゲートリレー(G型) ゲート用。動作時間は他の型に比べて速くなくてよいが、多接点であること、消費電力がなるべく少ないことが求められた。 |

1955年、富士通信機製造(当時)製

使用電圧:直流 60 V

接点電流の許容限界:500 mA

接点はすべて双子接点

日本初の実用大型リレー(継電器)式計算機であるETL Mark Ⅱのリレーユニットです。電磁石を使った電磁式のスイッチであるリレーを用いた計算機の研究は1935(昭和10)年代から日本の国内でも始まりました。電気試験所(現:産業技術総合研究所)の駒宮安男や末包良太らは、試作機ETL Mark Ⅰを経て、1955(昭和30)年に実用大型機のETL Mark Ⅱを完成させました。制御方式は将棋倒し方式と呼ばれた方法で、前段のリレーの動作完了信号により次段のリレーが動作を開始する完全な非同期式です。